The cPC2PMC is a hot swappable CompactPCI<sup>®</sup> PMC carrier. Two PMC module sites are provided. It is possible to remove the cPC2PMC and associated PMC modules from a powered CompactPCI<sup>®</sup> system without having to power down the system first. Currently the Hot Swap features are fully supported under Windows2000 and XPEmbedded.

# **Key Features**

- CompactPCI<sup>®</sup> Specification 2.0 R3.0.

- CompactPCI<sup>®</sup> Hot Swap Specification 2.1 R1.0.

- Two PMC sites conforming to PMC standard IEEE P1386.1/Draft 2.0 4<sup>th</sup> April 1995.

- PMC on CompactPCI<sup>®</sup> Specification 2.3 R1.0.

- Texas Instruments PCI2250 33MHz 32-bit PCI bridge conforming to PCI local bus specification 2.2.

- Compliant with PCI Bus Power Management Specification Revision 1.1.

- Compliant with Advanced Configuration and Power Interface (ACPI) 1.0.

- Compliant with PICMG Compact Hot Swap Specification Revision 1.0.

- Power to both PMC sites controlled by single chip Hot Swap controller (Linear Technology LTC1643).

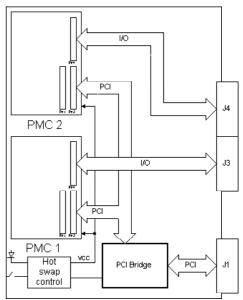

- PMC rear I/O via J3 & J4 (J3 and J5 on cPC2PMC-T).

#### Hot Swap

Hot swap is activated by opening the handles on the front of the CompactPCI module. This interrupts the processor and the hot swap software unloads the associated drivers for the PMC modules and PCI bridge and switches on the blue LED indicating that it is safe to remove the module. As the cPC2PMC is extracted from its slot the PMC sites are powered down first ensuring there are no switching glitches. As the card is removed from its slot the last thing to power down is the PCI bridge. Re-installation is the reverse process.

## **CompactPCI<sup>®</sup> Interface**

The CompactPCI<sup>®</sup> interface on the cPC2PMC is implemented using a Texas Instruments PCI2250 PCI-to-PCI bridge. This provides a high performance connection path between the CompactPCI<sup>®</sup> bus and the on-board PCI bus. Transactions occur between masters on one PCI bus and targets on another PCI bus, and the PCI2250 allows bridged transactions to occur concurrently on both buses. The bridge supports burst-mode transfers to maximise data throughput, and the two bus traffic paths through the bridge act independently.

The PCI2250 bridge is compliant with the PCI Local Bus Specification, overcoming the electrical loading limits on the PCI bus by creating hierarchical buses. The PCI2250 provides two-tier internal arbitration for the secondary bus masters.

The PCI2250 provides CompactPCI<sup>®</sup> (CPCI) hot-swap extended capability allowing live insertion and extraction of the cPC2PMC CompactPCI<sup>®</sup> Hot Swap Dual PMC Carrier.

The PCI2250 bridge is compliant with the PCI-to-PCI Bridge Specification. It can be configured for positive decoding or subtractive decoding on the primary interface. Two extension windows are included, and the PCI2250 provides decoding of serial and parallel port addresses.

The PCI2250 is compliant with PCI Power Management Interface Specification Revisions 1.0 and 1.1.

## PCI2250 Features

- Configurable for PCI Power Management Interface Specification Revision 1.0 or 1.1 support.

- CompactPCI<sup>®</sup> friendly silicon as defined in the CompactPCI<sup>®</sup> Hot Swap Specification.

- 3.3V core logic with universal PCI interface compatible with 3.3V and 5V PCI signalling environments.

- Two 32-bit, 33-MHz PCI buses.

- Provides internal two-tier arbitration for secondary bus masters.

- Burst data transfers with pipeline architecture to maximise data throughput in both directions.

- Provides programmable extension windows and port decode options.

- Independent read and write buffers for each direction.

- Provides five secondary PCI clock outputs.

- Predictable latency per PCI Local Bus Specification.

- Propagates bus locking.

- Secondary bus is driven low during reset.

- Provides VGA palette memory and I/O, and subtractive decoding options.

- Advanced sub-micron, low-power CMOS technology.

- Fully compliant with PCI-to-PCI Bridge Architecture Specification.

#### **Bus Connection**

The cPC2PMC can be used in an eight slot or less CompactPCI<sup>®</sup> enclosure with either 3.3V or 5V VI/O without any setting changes. The CompactPCI<sup>®</sup> VI/O setting has no effect on the PMC sites. The cPC2PMC is a 32-bit 33MHz CompactPCI<sup>®</sup> module and can be used in standard, Hot Swap or High Availability enclosures.

### **PMC Sites**

Two 32-bit 33MHz PMC sites are provided. These sites conform to "Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC, IEEE P1386.1/Draft 2.0 April 4, 1995" and "Draft Standard for a Common Mezzanine Card Family: CMC IEEE P1386/Draft 2.0 April 4, 1995". The Power for the PMC modules is link selectable at either 3.3 or 5 volts.

### **Hot Swap Controller**

The cPC2PMC uses a Linear Technology LTC<sup>®</sup> Hot Swap controller that allows the cPC2PMC to be safely inserted and removed from a live CompactPCI<sup>®</sup> slot. Four external transistors control the 3.3V, 5V, 12V and -12V supplies. All supply voltages are ramped up at a controlled rate to prevent any current glitches.

An electronic circuit breaker protects all four supplies against overcurrent faults. The foldback current limit feature limits current spikes and power dissipation when shorts occur and the cPC2PMC to be powered up without tripping the circuit breaker.

The PWRGD output indicates when all of the supply voltages are within tolerance and drives the CompactPCI<sup>®</sup> HEALTHY# signal. The ON pin is driven from the CompactPCI<sup>®</sup> BD\_SEL# signal and is used to cycle the board power or reset the circuit breaker.

# LTC<sup>®</sup> 1643L Features

- Allows safe board insertion and removal from a live CompactPCI<sup>®</sup> slot.

- Controls 3.3V, 5V, 12V, -12V supplies.

- Foldback current limit with circuit breaker.

- Ramped supply voltage power-up.

- High-side drive for external N-channels.

- Fault and power-good outputs.

### **Ejector Handle Switch Operation**

The cPC2PMC uses a microswitch built in to the lower front-panel ejector/injector handle. A change of state in the microswitch will occur during an insertion and extraction from a CompactPCI<sup>®</sup> backplane. This will cause the ENUM# signal to be asserted on the CompactPCI<sup>®</sup> backplane. This signal is used by the master CPU to instigate a hot swap procedure.

### **Front Panel LED Indicators**

The front panel contains a total of nine LED indicators showing which PMC site is bus master, what voltages are selected, read and write activity and the blue Hot Swap indicator.

# **BVM Limited**

Hobb Lane Hedge End Southampton SO30 0GH UK

Tel: +441489 780144 Fax: +44 1489 783589

www.bvmltd.co.uk

Email: sales@bvmltd.co.uk